From Concept to Custom Architecture

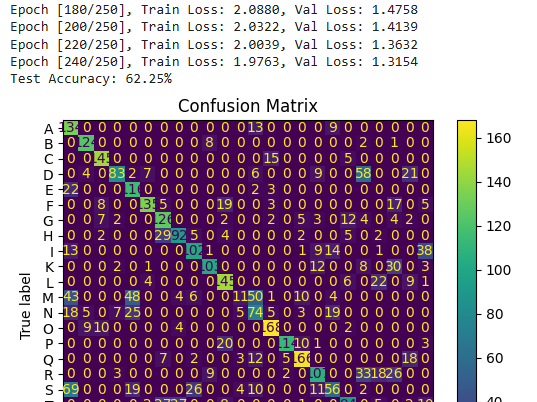

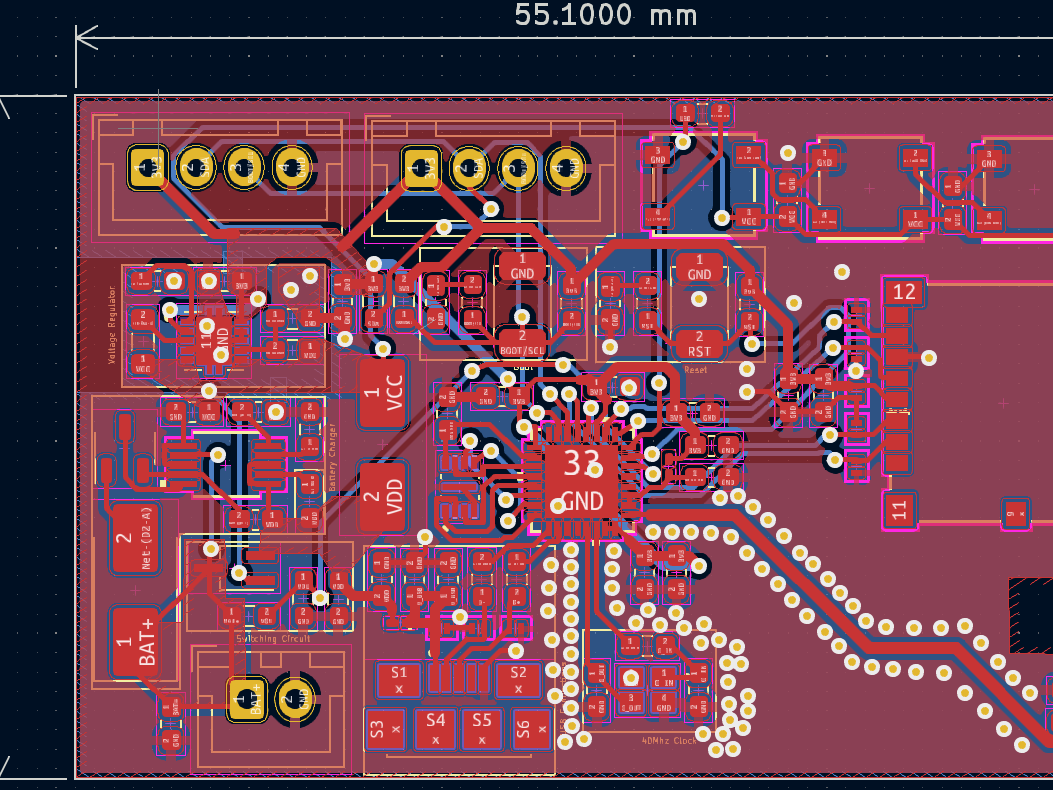

Our team set out to build a fully functional 32-bit RISC-V processor on an FPGA, starting from the fundamentals of instruction set architecture. We designed the CPU around the RISC-V base instructions and the RV32M extension, defining our own control logic, pipeline stages, and data paths. I was responsible for the control logic, overall architecture, and all supporting logic blocks except the ALU, carefully coordinating instruction decoding, memory access, and execution. The process involved iterative design and testing, where each stage of the pipeline had to be validated for correct instruction handling and latency optimization.

Expanding and Interfacing with the World

Once the core CPU was stable, I extended it with custom I/O and a UART module to enable real-time communication with external devices. This required writing a custom UART driver tailored to our architecture and creating testbenches to verify proper operation under live conditions.

Through waveform analysis, debugging, and ISA compliance checks, we refined the processor for reliable execution and efficient throughput. The project not only resulted in a fully working RISC-V processor on FPGA but also provided a foundation for future architectural experiments, peripheral integration, and performance enhancements.